Signal Integrity Simulation

Signal integrity simulation test

WHY Signal Integrity (SI) Simulation?

In low-speed signal transmission interfaces, we rarely encounter serious signal quality problems. However, with the continuous increase in high-speed signal transmission speed and the increasing complexity of chip, package, and passive component designs, you may encounter potential problems such as reflection, distortion, delay, crosstalk, and impedance mismatch. These problems can seriously damage signal transmission. Therefore, signal integrity has gradually become an indispensable part of the product design and development process.

WHAT Benefits of Signal Integrity(SI) Simulation?

With the rapid development of artificial intelligence, machine learning, 5G, automotive, and the Internet of Things, the design cycle of electronic products is becoming increasingly shorter, making time-to-market (TTM) a key factor in today's competitive market. Signal integrity (SI) analysis helps identify potential high-speed signal issues in the early design phase (kick-off) and develop corresponding high-speed layout constraints to avoid unexpected signal transmission problems before testing and manufacturing.

WHEN Do You Need Signal Integrity (SI) Analysis?

When you use high-speed signals and high-speed transmission interfaces such as PCIe, USB, SATA, etc. in chips, packages, or printed circuit boards (PCBs), signal integrity in high-speed designs should be a primary consideration.

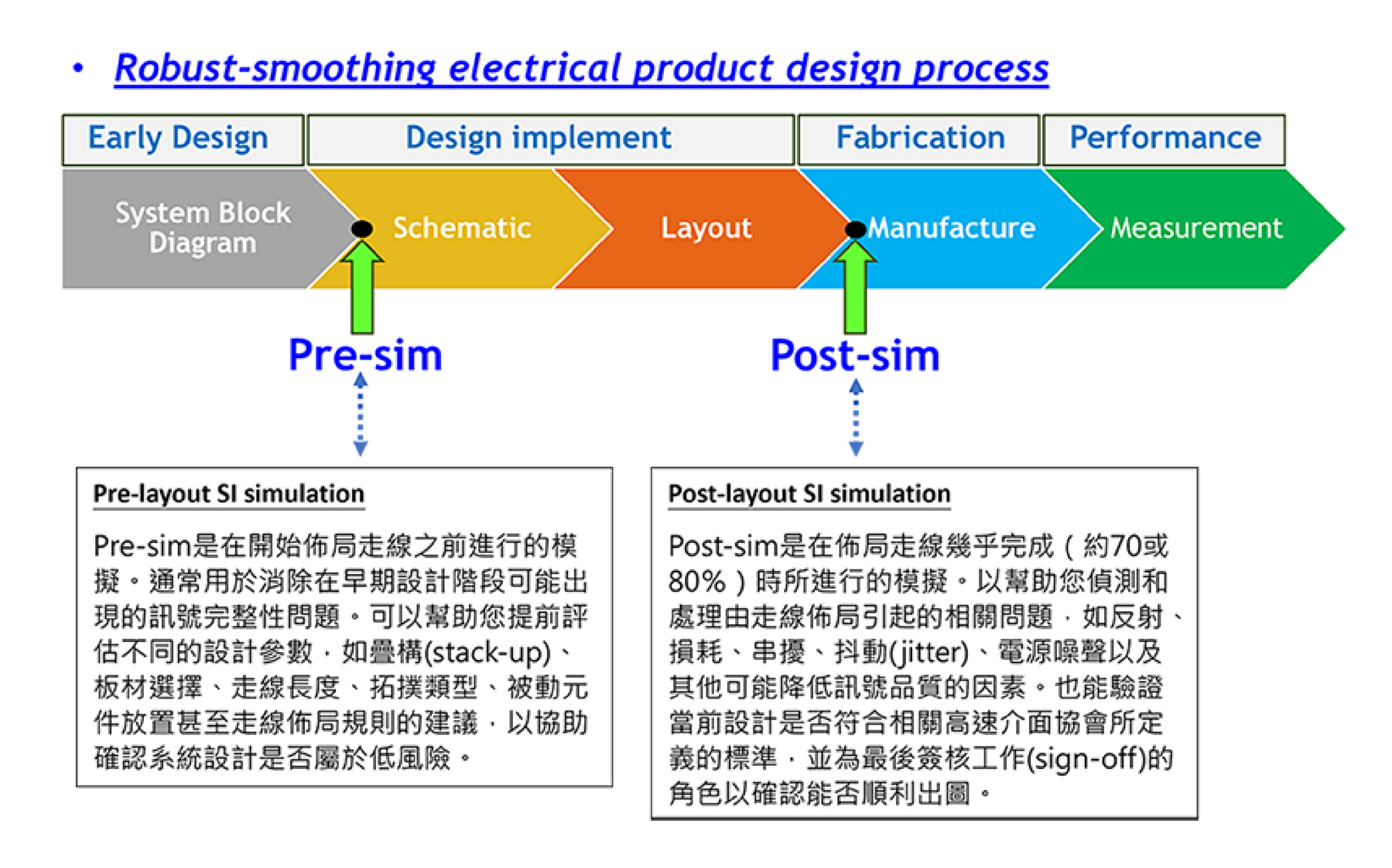

iPasslabs | Signal integrity analysis simulation testing during the project design phase is divided into two types.

iPasslabs | Signal integrity analysis simulation testing during the project design phase is divided into two types.

iPasslabs | Frequently Asked Questions

1. If a formal simulation analysis project is to be conducted, what materials are required?

Stackup (Stacked Configuration):

Provides PCB stackup information, including the number of layers, material type of each layer, thickness, etc.

Package Model:

The electrical characteristics of an IC package include information about the package's parasitic elements, such as capacitors, inductors, and resistors.

Connector Model:

If the system includes connectors, please provide the correct connector S-parameter model. This helps ensure the connector's performance analysis during high-speed data transmission, enabling the provision of a complete and accurate report.

Chip and Device IBIS/IBIS-AMI/DLL Models:

If IBIS (Input/Output Buffer Information Specification/Non-SerDes), IBIS-AMI (Algorithmic Model Interface/SerDes) models and DLLs are used

The (Dynamic Link Library) model requires corresponding model files to describe the input/output buffer behavior of the chip and device in order to provide the best eye diagram and EQ effect for simulation analysis.

Design Guide:

Provide any relevant design guidelines or advisory documents that offer the best actionable recommendations for a specific simulation project.

2. Is it possible to perform simulation analysis only on the longest line segment in the configuration design drawing?

Yes, it's possible. Signal quality analysis (SI) simulations typically use the worst-case scenario for evaluation. However, we recommend including the shortest line in the analysis as well, because the longest and shortest lines represent the worst-case scenarios for insertion loss and return loss, respectively. This provides a more complete and accurate signal quality analysis, improving product yield.

3. How is the simulation analysis performed, and how long does a single session typically take?

Describe the project or answer questions to provide more information to interested website visitors. You can emphasize this text with bullet points, italics, or bold. Essentially, both pre-sim and post-sim analysis results will provide suggestions on how to optimize the configuration design. After the client modifies according to the suggestions, we can provide a second verification. One topology takes approximately one week of working days.

。

4. How is the price calculated?

Pricing is based on system size (block diagram). For further details, please contact the relevant contact person.