Power Integrity (PI) Simulation

電源完整性模擬測試

WHY Signal Integrity (SI) Simulation?

基本的電子系統設計需要一組或多組電源供應電壓來運作。這些供應電壓通常需透過電壓調節模組(VRMs)來轉換取得。電壓調解模組被設計用來為各種的負載提供所需的工作電壓。電源供應及其傳輸路徑必須滿足負載電壓的漣波要求。電源完整性分析可以評估電源分配網路(PDN)的壓降和電源噪聲,來幫助您優化整個電源層,以確保產品正常運行。

WHAT Benefits of Power Integrity (PI) Simulation?

隨著電源供應電壓持續降低,以及電晶體數量遵循摩爾定律持續增長,電源分配網絡(PDN)設計已經成為任何電子產品必須考量的重要因素。不良的PDN設計會導致產品中出現過大的壓降和電源雜訊。通過電源完整性(PI)模擬來預測PDN性能以確保電子產品電源正常運作並滿足電池壽命,其為重要。

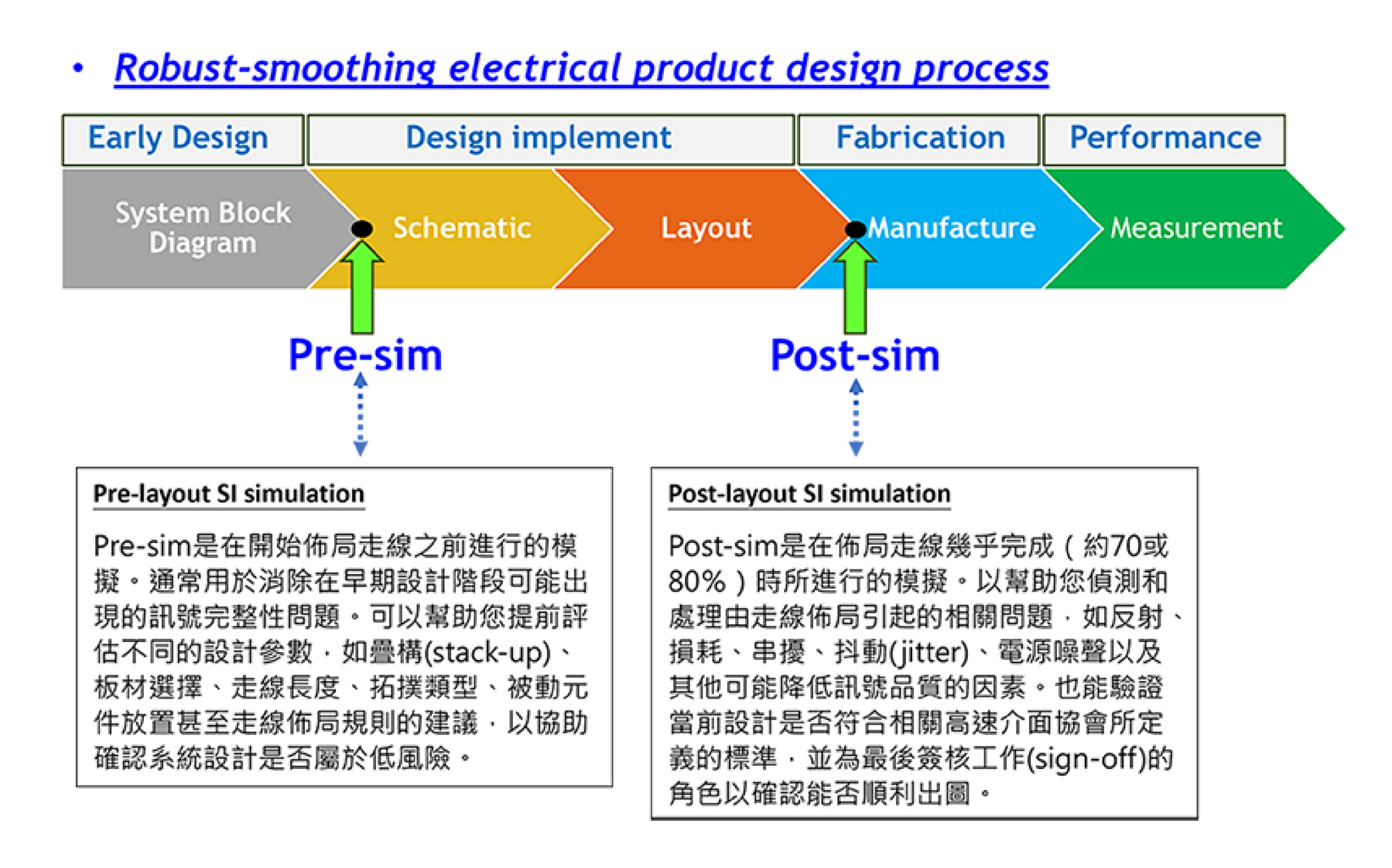

WHEN Do You Need Signal Integrity (SI) Analysis?

當您在晶片(chip)、封裝(package)或印刷電路板(PCB)中使用高速訊號和高速傳輸介面,如PCIe、USB、SATA等等時,高速設計的訊號完整性應該是首要考慮的事項。

iPasslabs|在專案設計階段訊號完整性分析模擬測試有分為兩種

iPasslabs|在專案設計階段訊號完整性分析模擬測試有分為兩種

iPasslabs|常見問題

1.如果正式進行模擬分析專案,請問需要提供那些資料?

Stackup(堆疊配置):

提供 PCB 的 stackup 資訊,包括板層數、每層材料類型、厚度等。

Package Model(封裝模型):

IC封裝的電氣特性,它包括有關封裝的寄生元件,如電容、電感和電阻的訊息。

Connector Model(連接器模型):

如果系統中包含連接器,請提供正確的連接器S參數模型。這有助於確保連接器在高速數據傳輸中的性能分析,才能提供完整且正確的報告。

Chip and Device IBIS/IBIS-AMI/DLL Models(晶片和設備 IBIS/IBIS-AMI/DLL 模型):

如果使用了 IBIS (Input/Output Buffer Information Specification/Non-SerDes) 、IBIS-AMI (Algorithmic Model Interface/SerDes)模型及DLL

(Dynamic Link Library)模型,需提供相應的模型文件,以描述晶片和設備的輸入/輸出緩衝器行為,才能提供最佳眼圖以及EQ效應去進行模擬分析。

Design Guide(設計指南):

提供任何相關的設計指南或建議文件,這些文件可以針對特定模擬專案提供最佳可執行的建議。

2. 是否可以只針對配置設計圖最長的線段來做模擬分析

可以。通常SI模擬都是採取the worst case來評估,不過會建議您也把最短的線併入一起分析, 因為最長和最短分別是插入損耗(Insertion loss)和反射損耗(Return loss) 的the worst case,訊號品質分析結果較完整且更正確,提高產品良率.

3. 請問模擬分析是如何執行,單次時間大約為多久?

描述項目或回答問題,以便有興趣的網站訪客獲得更多信息。 您可以用項目符號、斜體或粗體強調此文字,並加入基本上,無論是pre-sim或是post-sim分析結果都會提供如何優化配置設計圖的建議,客戶可依照建議修改後, 我們可以再提供驗證一次。一個topology約為一個禮拜工作日。

。

4. 請問價格如何計算?

視系統大小(block diagram)來提供價格,欲了解進一步細節,請詢洽相關窗口。